芯片,又称微电路(microcircuit)、微芯片(microchip)、集成电路(integrated circuit, IC),是指内含集成电路的硅片,体积很小,常常是计算机或其他电子设备的一部分。

芯片(chip)就是半导体元件产品的统称,是 集成电路(IC, integrated circuit)的载体,由晶圆分割而成。

硅片是一块很小的硅,内含集成电路,它是计算机或者其他电子设备的一部分。

2023年4月,国际科研团队首次将能发射纠缠光子的量子光源完全集成在一块芯片上.

电路制造在半导体芯片表面上的集成电路又称薄膜(thin-film)集成电路。另有一种厚膜(thick-film)集成电路(hybrid integrated circuit)是由独立半导体设备和被动组件,集成到衬底或线路板所构成的小型化电路。

集成电路根据微电子器件的数量分类

-

小型集成电路(SSI英文全名为Small Scale Integration)逻辑门10个以下或晶体管100个以下。

-

中型集成电路(MSI英文全名为Medium Scale Integration)逻辑门11~100个或 晶体管101~1k个。

-

大规模集成电路(LSI英文全名为Large Scale Integration)逻辑门101~1k个或 晶体管1,001~10k个。

-

超大规模集成电路(VLSI英文全名为Very large scale integration)逻辑门1,001~10k个或 晶体管10,001~100k个。

-

极大规模集成电路(ULSI英文全名为Ultra Large Scale Integration)逻辑门10,001~1M个或 晶体管100,001~10M个。

-

GLSI(英文全名为Giga Scale Integration)逻辑门1,000,001个以上或晶体管10,000,001个以上。

模拟集成电路和数字集成电路

计算机芯片根据功能分为四大类

存储器芯片

存储器芯片用于将程序和数据存储在计算机和存储设备上。RAM 芯片提供临时存储,而闪存驱动器和固态硬盘(SSD)可以永久保存信息。闪存单元即使在电流关闭时也可以存储数据。

逻辑芯片

逻辑芯片或处理器芯片用于处理数据以完成任务。它们相当于现代电子设备的大脑。CPU 是服务器和其他计算硬件的微处理器中的主要逻辑芯片类型。但也可以针对特定功能设计逻辑芯片。下面是一些示例:

- 图形处理单元设计用于优化视觉显示

- 神经处理单元设计用于深度学习和机器学习应用程序

ASIC

专用集成芯片(ASIC)设计用于为特定应用程序执行重复处理例程。这些现代芯片大批量生产,用于条形码扫描仪等单一用途设备。另一个示例是比特币挖矿,在该过程中,ASIC 执行生成新比特币所需的复杂数学例程。

SoC

片上系统(SoC)是一种较新类型的芯片。整个系统所需的所有电子元件都内置于一个芯片中。SoC 的功能比微控制器更广泛。微控制器通常将 CPU 与存储器和 I/O 处理相结合。但 SoC 可以集成图形、音频、摄像头和视频处理。

芯片制造

-

光刻

-

刻蚀

-

薄膜(化学气相沉积或物理气相沉积)

-

掺杂(热扩散或离子注入)

-

化学机械平坦化CMP

-

在一个自排列(CMOS)过程中,所有门层(多晶硅或金属)穿过扩散层的地方形成晶体管。

-

电阻结构,电阻结构的长宽比,结合表面电阻系数,决定电阻。

-

电容结构,由于尺寸限制,在IC上只能产生很小的电容。

-

更为少见的电感结构,可以制作芯片载电感或由回旋器模拟。

芯片制造过程

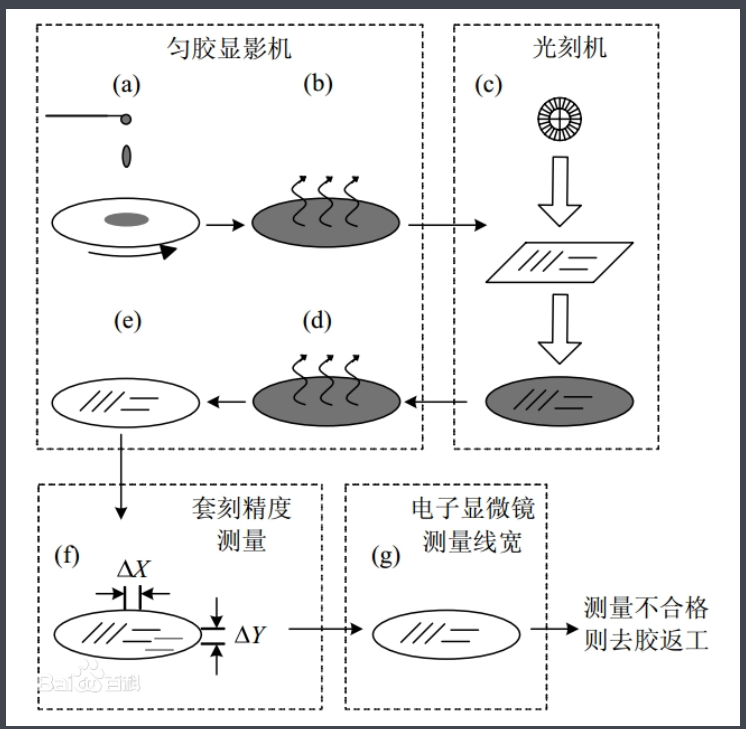

首先是在晶圆(或衬底)表面涂上一层光刻胶并烘干。烘干后的晶圆被传送到光刻机里面。光线透过一个掩模把掩模上的图形投影在晶圆表面的光刻胶上,实现曝光,激发光化学反应。对曝光后的晶圆进行第二次烘烤,即所谓的曝光后烘烤,后烘烤使得光化学反应更充分。最后,把显影液喷洒到晶圆表面的光刻胶上,对曝光图形显影。显影后,掩模上的图形就被存留在了光刻胶上。涂胶、烘烤和显影都是在匀胶显影机中完成的,曝光是在光刻机中完成的。匀胶显影机和光刻机一般都是联机作业的,晶圆通过机械手在各单元和机器之间传送。整个曝光显影系统是封闭的,晶圆不直接暴露在周围环境中,以减少环境中有害成分对光刻胶和光化学反应的影响。

计算机芯片的工作原理是什么?

计算机芯片的工作方式是通过电路元件来传输电信号。

模拟集成电路

模拟电路在给定的时间段内传输连续、变化的信号。输出信号是输入的线性函数,二者电压成正比。这种类型的集成电路用于计时器、比较器、电压调整器和运算放大器等设备功能。模拟芯片用于扫描发生器、振荡器、音频放大器和滤波器。

数字集成电路

数字电路传输不连续或二进制信号。输出电压可高可低。高电压代表布尔值 1,低电压代表值 0。

数字电路设计用于执行不同的逻辑运算,如 AND(与)、OR(或)和 NAND(与非)。例如,逻辑 OR(或)运算对应于布尔加法,是计算机加法运算的基础。因此,数字集成电路构成了所有计算操作的基础。它们对于所有可编程设备、逻辑板、微控制器和存储器都至关重要。

混合信号集成电路

混合芯片结合了模拟和数字芯片的元素。混合设计使得此类芯片能够充当数模和模数转换器。这些先进集成电路是现代计算的另一种核心组件。

量子电路

量子电路是计算发展的下一个阶段。量子电路是一种计算例程,它定义了对底层量子位(或量子比特)的一系列逻辑量子操作。量子位通过量子粒子表示,不同于布尔数字信号。布尔信号是 1 或 0,而量子位可以处于多种状态的叠加态。包含量子电路的芯片构成了量子计算的基础,它是一种新兴技术。

主要晶圆代工厂

主要晶圆代工厂有格罗方德、三星电子、Tower Jazz、Dongbu、美格纳、IBM、富士通、英特尔、海力士、台积电、联电、中芯国际、力晶、华虹、德茂、武汉新芯、华微、华立、力芯

纳米制程是什么?

纳米是什么米?纳米是用于测量长度的测量单位。1纳米等于一米的十亿分之一,因此,纳米绝对不是用来测量长距离的。相反,它们用于测量极小的物体,例如现代CPU中的原子结构或晶体管,单个纳米比毫米小一百万倍。所以,纳米非常小。

芯片中晶体管是什么结构?任何芯片、IC、处理器、内存或GPU都是由大量晶体管的集成制成的。由于此类芯片是在内部集成了大量晶体管制成的,通常将其称为IC(集成电路)。并且根据制造这种芯片组的集成晶体管的数量,将它们分为SSI(小规模集成),LSI(大规模集成)或VLSI(超大规模集成)。晶体管由于集成电路(例如计算机处理器)包含微观组件,因此纳米对于测量其尺寸非常有用。实际上,纳米定义了不同的处理器时代,代表处理器(芯片)制造工艺的不同工艺阶段,这基本上是一种工艺技术,其中包括所涉及的制造工艺(如光刻)和物理参数(如尺寸和厚度)等,其中数字定义了晶体管与CPU中其他组件之间的距离。

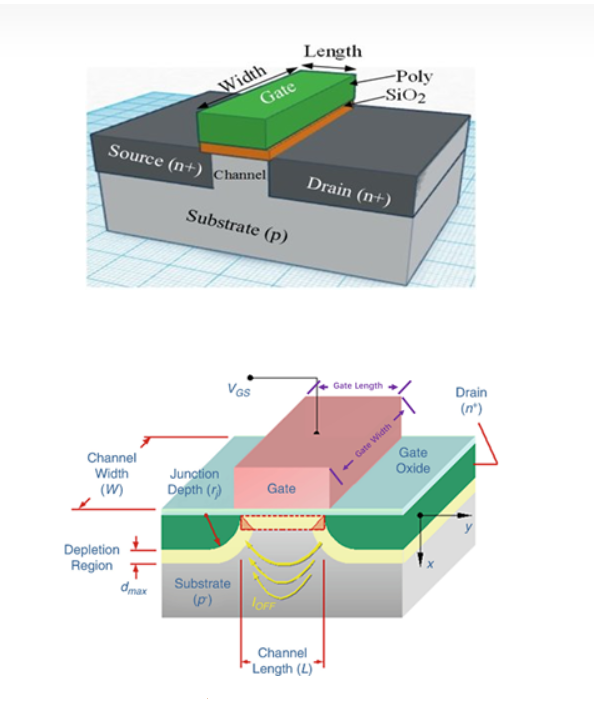

我们知道芯片由晶体管所组成,晶体管由源极、漏极和位于它们之间的栅极所组成,而平面制程工艺尺寸就是指源极到漏极的沟道长度,近似于栅极长度。

源极 = Source 漏极 = Drain 栅极 = Gate

但是随着技术演进,类似FinFET的空间结构晶体管出现,沟道长度已经不能代表工艺的最高精度。

那么区别于传统工艺,在FinFET工艺节点上,现在的定义是源极到漏极的空间距离(这个距离小于实际channel的电荷移动距离)。但现在的沟道长度并不好测量,它会根据掺杂扩散,大小尺寸不一,而栅极长度近似沟道长度,且栅极长度观察测量更为直观,因此采用栅极长度作为制程工艺参考标准。

沟道长度 = Channel Length 栅极长度 = Gate Length

因此我们常听到的芯片7nm、5nm,这个数字指的就是沟道长度,但由于它不容易观测,且栅极长度更直观并近似沟道长度(栅极长度>沟道长度),所以一般约定俗成可以将其理解为栅极长度。

晶体管实质上由漏极(Drain),源极(Source)和栅极(Gate)组成。在源极和漏极之间有一条使电子(从而电流)流动的路径,称为通道。Gate负责控制通道的宽度。通道越宽,电子在通道中流动的速度越慢,反之亦然。处理器中提到的纳米技术是通道之间平均距离的度量。晶体管越小,源极与漏极之间的距离越小,形成栅极下方的导电沟道所需的电子或空穴的数量就越少。需要较小的输入电压以产生较少的功耗,栅极的最小宽度就是工艺制程中的X纳米。

处理器架构——纳米技术:任何芯片,无论是处理器,内存还是GPU,都是通过集成大量晶体管制成的。晶体管只是电子信号的开关,具有两种状态(ON/OFF)。纳米架构是晶体管的大小。尺寸越小,可将更多晶体管嵌入到处理器芯片中,从而增加其计算量。45nm,32nm,28nm,14nm,10nm和7nm基本上是采用新制造技术的晶体管的缩放比例。芯片的长度越短,电流(或信息)可以流过的速度就越快。同样,较短的芯片消耗的电压更少。

为什么纳米小一点好?

过程节点的大小(以纳米为单位)描述了芯片最小可能元素的大小。可以这样想象:如果芯片的设计是数字图像,则一个”像素”的大小将是处理大小。制程越小,可获得的分辨率越高。制造商可以使晶体管和其他组件更小。这意味着更多的晶体管可以塞满较小的物理空间。

在给定的空间中可以容纳的晶体管越多,处理能力就越大。芯片组上使用的每个晶体管都将具有较小的尺寸。因此,可以在芯片组内部封装更多数量的晶体管,这些晶体管的尺寸与以较大纳米距离制造的芯片组的尺寸相同。如果平均缩小晶体管的所有部分,则该晶体管的电性能不会改变。

在小型芯片组中制造大量晶体管的设施可提供更多功能。

较小的晶体管速度更快,这使它们可以以更高的时钟速率工作。这样可以提高性能。这是由于计算并行性和缓存大小的增加。因此,如果希望加快芯片速度或添加新功能,则最好的办法是缩小其晶体管的尺寸。

较小的工艺也具有较低的电容,从而允许晶体管以更少的能量更快地打开和关闭。晶体管可以打开和关闭的速度越快,它的工作速度就越快。以更少的能量导通和截止的晶体管效率更高,从而降低了处理器所需的工作功率或”动态功耗”。动态功耗较低的芯片将使电池耗电更慢,运行成本更低并且更加生态友好。

较小的芯片也更便宜。芯片是在圆形硅晶片上制成的。一个晶圆通常将包含数十个处理器管芯。较小的工艺尺寸将产生较小的管芯尺寸。而且,如果管芯尺寸较小,则可以在单个硅晶片上安装更多管芯。这导致制造效率的提高,降低了制造成本。开发新工艺确实需要大量投资,但是在收回成本之后,每个芯片的成本将大大下降。

较小的工艺规模有何弊端?

散热。尺寸较小时,由晶体管产生的热量将具有较小的散热面积,这可能会导致芯片组过热。

较小的晶体管更难制造。随着晶体管的缩小,制造以尽可能高的时钟速度运行的芯片变得越来越困难。一些芯片将无法以最高速度运行,并且这些芯片将被”绑定”或标记为具有较低时钟速度或较小缓存的芯片。较小的工艺通常会以较低的时钟速度合并更多的芯片,因为制作”完美”的芯片更具挑战性。制造商小心翼翼地消除尽可能多的问题,但这通常归因于模拟世界不可避免的变化。

较小的晶体管也具有更大的”泄漏”。泄漏是晶体管在”关”位置时允许通过多少电流的度量。这意味着随着泄漏的增加,静态功耗或晶体管空闲时消耗的电量也会增加。泄漏量更大的芯片即使在不活动时也需要更多的功率,从而更快地消耗电池并降低运行效率。

较小的过程可能会降低产量,从而导致更少的全功能芯片。这可能导致生产延迟和短缺。这使得收回开发新工艺所需的投资更加困难。这种风险因素是任何新制造工艺的基础,但对于像半导体制造这样精确的工艺而言,风险尤其如此。

为什么纳米对智能手机如此重要?

移动互联网的飞速发展,带动了半导体行业的科技进步。在芯片制造领域,智能手机芯片的制作工艺和进度,大幅度的领先于传统的PC行业,是极具代表性的产业。追求更好、更快、更小的芯片是智能手机芯片不断前行的目标,这里就纳米对智能手机的影响展开。

谈论智能手机之绕不开的话题:纳米?在智能手机的世界中,不断看到终端制造厂商互相竞争,每年都在配备最新的X纳米处理器的同时发布旗舰智能手机。旗舰产品或任何智能手机必须具备的关键功能是性能、功耗和散热,在此基础上它应具有无滞后,快速且高效的界面,而这些都与”纳米”有关。智能手机的性能取决于各种因素,例如应用程序优化、RAM大小、操作系统和处理器的优化,而这其中,处理器的性能是重中之重,芯片制程工艺的数值是旗舰机比对的关键性能指标,相当于一个水杯的容量,决定着可以装多少水。下图统计了近年来Android手机在安兔兔上的跑分,但就芯片比对而言,制程的进步的确带来了性能的飞跃(蓝色:旗舰机,黄色:中端机,红色:低端机)。

移动处理器头痛的心脏健康指数——”纳米”,工艺节点越小,意味着更高的性能、更低的功耗和更高的集成度,也就意味着单位生产力更高,智能手机的心脏——芯片更强。

为什么晶体管之间的距离,纳米很重要?智能手机是便携式设备,这意味着它的空间有限,只能有限地容纳其硬件部件。所以不能使用标准的计算机和笔记本电脑处理器,因为它们的尺寸很大,这意味着需要更好的散热系统,这只会有一个结果——”空间不足!”。因此,许多公司已经开发了非常小的间距晶体管,以适合纳米面积的小型处理器,从而使其与智能手机兼容。移动处理器中的是处理器内部晶体管之间的最短距离。高通、三星、联发科、华为和苹果是为智能手机开发”纳米”移动处理器的领先公司。近年来,移动处理器中的”纳米”计数一直在从12纳米减少到10纳米再到7纳米(高通骁龙865、华为麒麟990)。纳米制造工艺术语定义了处理器的尺寸。使用20nm晶体管,可以将大约2500亿个晶体管安装在指甲大小左右的硅晶片上。比如说有一个盒子可以容纳100个大小为10cm的橡皮擦,每个橡皮擦之间相距1cm。如果减少橡皮擦之间的长度,我们可以容纳更多的橡皮擦吧?在移动处理器中的纳米后面使用类似的逻辑。同样,如果减小处理器中晶体管之间的距离,则可以安装更多的晶体管。更多的晶体管紧密堆叠在一起,这意味着在减少处理的同时电子的传播路径。这意味着更快的处理能力,更少的热量产生和低功耗。因此,移动处理器中的纳米越小,效率和功能就越强大。

高通公司的Snapdragon 855是在7纳米FinFET处理器上设计的,与10纳米芯片相比,可提供高达45%的性能提升或25%的功耗降低。

晶体管可以看做是单个处理单元,制程越小,可以在同一区域内放置的晶体管就越多,芯片中晶体管集成度就越高,从而可以进行更快,更高效的芯片设计,芯片中的晶体管数量倾向于确定芯片的处理能力。