在半导体制造领域,3纳米工艺是继5纳米MOSFET(金属氧化物半导体场效应晶体管)技术节点之后的下一次缩小芯片尺寸的工艺。韩国芯片制造商三星于2022年年中开始出货其3纳米栅极全包域(GAA)工艺,被称为3GAA[1][2]。而在2022年12月29日,台湾芯片制造商台积电宣布其3纳米半导体工艺(称为N3)的大规模生产已经开始,并且产量良好[3]。一种升级版的3纳米芯片工艺,名为N3E,可能会在2023年开始生产[4]。美国制造商英特尔计划在2023年开始生产3纳米工艺的芯片[5][6][7]。

三星的3纳米工艺基于GAAFET(全包域场效应晶体管)技术,这是一种多栅MOSFET技术,而台积电的3纳米工艺仍然使用FinFET(翼式场效应晶体管)技术[8],尽管台积电正在研发GAAFET晶体管[9]。具体来说,三星计划使用自己的GAAFET变种,被称为MBCFET(多桥道场效应晶体管)[10]。英特尔的工艺被称为“英特尔3”,没有“纳米”后缀,将使用改进、增强和优化版本的FinFET技术,以提高性能与功耗比、使用EUV光刻技术,以及提高功耗和面积的性能[11]。

“3纳米”这个术语与晶体管的实际物理特征(如栅极长度、金属间距或栅极间距)无关。根据IEEE标准协会工业协会发布的《国际器件与系统路线图》2021年更新中的预测,3纳米工艺节点预计具有48纳米的栅极间距和24纳米的最紧凑金属间距。

| 工艺 | 栅极间距 | 金属间距 | 年份 |

|---|---|---|---|

| 5 nm | 51 nm | 30 nm | 2020 |

| 3 nm | 48 nm | 24 nm | 2022 |

| 2 nm | 45 nm | 20 nm | 2024? |

然而,在实际商业实践中,“3 纳米”主要被各个微芯片制造商用作市场推广术语,用来指代一代新的、改进的硅半导体芯片,其特点是晶体管密度增加(即更高程度的微型化)、速度提高和功耗降低[13][14]。不同制造商之间并没有关于什么数字定义了3纳米工艺的行业共识。通常,芯片制造商会将其自己的前一代工艺节点(在这种情况下是5纳米工艺节点)作为比较基准。例如,TSMC已经表示,其3纳米FinFET芯片在相同速度下将减少25-30%的功耗,相同功耗下速度提高10-15%,晶体管密度比其前一代5纳米FinFET芯片提高约33%[15][16]。另一方面,三星表示,其3纳米工艺将减少45%的功耗,性能提高23%,并减少16%的表面积,相对于其前一代5纳米工艺[17]。在3纳米工艺下,EUV光刻面临新的挑战,这导致需要使用多重光刻技术[18]。

历史:

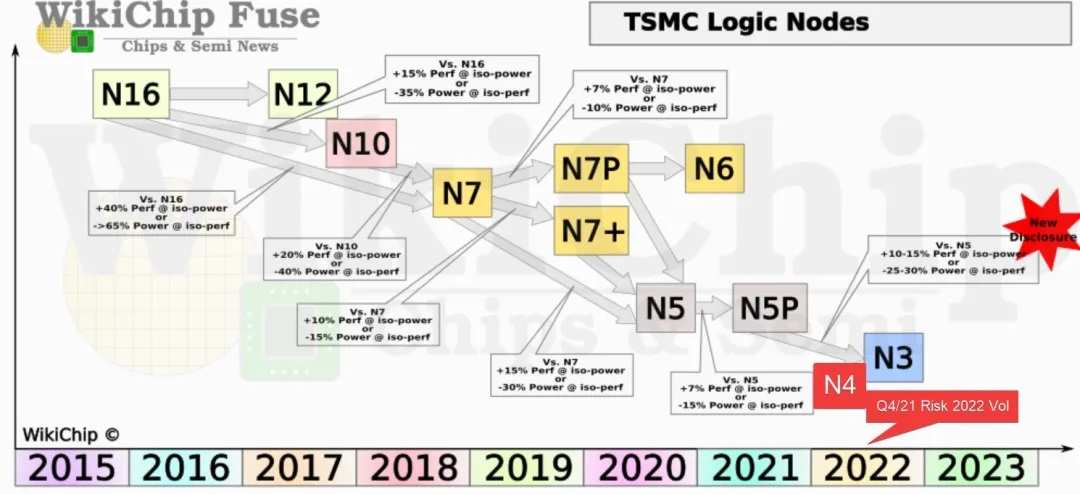

2017年9月29日,台积电宣布未来3纳米(nm)制程晶圆厂,落脚台湾台南市的南部科学工业园区,预计最快2022年量产。台积电于2020年第一季宣布3纳米制程将在2021年试产,并在2022下半年正式量产,其3纳米制程将继续采用FinFET(鳍式场效晶体管)。

2019年5月,三星表示其3纳米产品预计于2021年推出[3]。此后由于受到2019冠状病毒病疫情影响,三星的3纳米制程推出时程被延后到了2022年。

Intel在2019年泄漏的路线图显示,其3纳米制程预计在2025年推出。

2022年7月25日,三星宣布推出首款3纳米制程芯片,采用GAA FET(闸极全环场效晶体管)技术

据介绍,相较5nm N5工艺,相同功耗下,台积电3nm N3性能可提高10-15%;相同性能下,N3功耗可降低25-30%;N3的逻辑密度、SRAM密度、模拟密度分别是N5的1.7倍、1.2倍、1.1倍。

同时,台积电总裁魏哲家宣布,台积电已整合旗下包括SoIC、InFO、CoWoS等3D封装技术平台,命名为台积电3D Fabric。

台积电高级副总裁Kevin Zhang和Y.P. Chin在预先录制的视频中提到,台积电正在其总部旁边正建设一个专注于2nm芯片研发的新研发中心,拥有8000名工程师,将运营一条先进的生产线,该项目的第一阶段将于2021年完成。

作为全球晶圆代工「一号玩家」,从台积电的分享,我们可以看到全球先进制程最前沿的芯片制造技术风向。

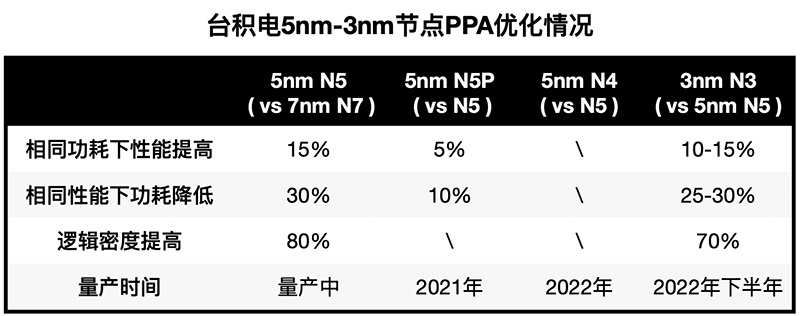

台积电介绍了5nm N5、N5P、N4工艺以及3nm N3工艺的PPA优化情况。

据悉,台积电5nm N5工艺广泛采用了EUV技术。相较7nm N7工艺,台积电N5工艺在相同功耗下的性能提高了15%,在相同性能下的功耗降低了30%,逻辑密度为N7的1.8倍。

台积电还提到,N5的缺陷密度学习曲线比N7快,这意味着5nm工艺将比其上一节点能更快地达到更高的良率。

N5P和N4属于5nm N5的增强版本。

N5P主要面向高性能应用,计划在2021年投入使用。与N5相比,同等功耗下,N5P的性能可提高5%;同等性能下,N5P的功耗可降低10%。

由于与N5节点在IP上兼容,因此台积电的5nm N4工艺可提供直接迁移,性能、功耗和密度均有所增强。台积电计划在2021年第四季度开始N4风险生产,目标是在2022年实现大批量生产。

相比5nm N5节点,台积电3nm N3在相同功耗下的性能可提高10-15%,在相同性能下的功耗可降低25-30%;逻辑密度提高70%,SRAM密度提高20%,模拟密度提高10%。

参考资料:

- “Samsung Begins Chip Production Using 3nm Process Technology With GAA Architecture” (Press release). Samsung. Archived from the original on 30 June 2022. Retrieved 30 June 2022.

- “History is made! Samsung beats out TSMC and starts shipping 3nm GAA chipsets”. 25 July 2022. Archived from the original on 23 August 2022. Retrieved 23 August 2022.

- “TSMC Kicks Off 3nm Production: A Long Node to Power Leading Chips”. Tom’s Hardware. 29 December 2022.

- Ramish Zafar (4 March 2022). “TSMC Exceeds 3nm Yield Expectations & Production Can Start Sooner Than Planned”. wccftech.com. Archived from the original on 16 March 2022. Retrieved 19 March 2022.

- Cutress, Dr Ian. “Intel’s Process Roadmap to 2025: with 4nm, 3nm, 20A and 18A?!”. AnandTech. Archived from the original on 3 November 2021. Retrieved 27 July 2021.

- Gartenberg, Chaim (26 July 2021). “Intel has a new architecture roadmap and a plan to retake its chipmaking crown in 2025”. The Verge. Archived from the original on 20 December 2021. Retrieved 22 December 2021.

- “Intel Technology Roadmaps and Milestones”. Intel. Archived from the original on 16 July 2022. Retrieved 17 February 2022.

- Cutress, Dr Ian. “Where are my GAA-FETs? TSMC to Stay with FinFET for 3nm”. AnandTech. Archived from the original on 2 September 2020. Retrieved 12 September 2020.

- “TSMC Plots an Aggressive Course for 3nm Lithography and Beyond – ExtremeTech”. Extremetech.com. Archived from the original on 22 September 2020. Retrieved 12 September 2020.

- “Samsung at foundry event talks about 3nm, MBCFET developments”. Techxplore.com. Archived from the original on 22 November 2021. Retrieved 22 November 2021.

- Patrick Moorhead (26 July 2021). “Intel Updates IDM 2.0 Strategy With New Node Naming And Transistor And Packaging Technologies”. Forbes. Archived from the original on 18 October 2021. Retrieved 18 October 2021.

- INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS™: More Moore, IEEE, 2021, p. 7, archived from the original on 7 August 2022, retrieved 7 August 2022

- “TSMC’s 7nm, 5nm, and 3nm “are just numbers… it doesn’t matter what the number is””. Pcgamesn.co. 10 September 2019. Archived from the original on 17 June 2020. Retrieved 20 April 2020.

- Samuel K. Moore (21 July 2020). “A Better Way to Measure Progress in Semiconductors: It’s time to throw out the old Moore’s Law metric”. IEEE Spectrum. IEEE. Archived from the original on 2 December 2020. Retrieved 20 April 2021.

- Jason Cross (25 August 2020). “TSMC details its future 5nm and 3nm manufacturing processes—here’s what it means for Apple silicon”. Macworld. Archived from the original on 20 April 2021. Retrieved 20 April 2021.

- Anton Shilov (31 August 2020). “The future of leading-edge chips according to TSMC: 5nm, 4nm, 3nm and beyond”. Techradar.com. Archived from the original on 20 April 2021. Retrieved 20 April 2021.

- “Samsung Begins Chip Production Using 3nm Process Technology With GAA Architecture”. 30 June 2022. Archived from the original on 8 July 2022. Retrieved 8 July 2022.

- Chen, Frederick (17 July 2022). “EUV’s Pupil Fill and Resist Limitations at 3nm”. LinkedIn. Archived from the original on 29 July 2022.

- Kobayashi, Toshio; Horiguchi, Seiji; Miyake, M.; Oda, M.; Kiuchi, K. (December 1985). “Extremely high transconductance (Above 500 mS/Mm) MOSFET with 2.5 nm gate oxide”. 1985 International Electron Devices Meeting. pp. 761–763. doi:10.1109/IEDM.1985.191088. S2CID 22309664.

- Ahmed, Khaled Z.; Ibok, Effiong E.; Song, Miryeong; Yeap, Geoffrey; Xiang, Qi; Bang, David S.; Lin, Ming-Ren (1998). “Performance and reliability of sub-100 nm MOSFETs with ultra thin direct tunneling gate oxides”. 1998 Symposium on VLSI Technology Digest of Technical Papers (Cat. No.98CH36216). pp. 160–161. doi:10.1109/VLSIT.1998.689240. ISBN 0-7803-4770-6. S2CID 109823217.

- Ahmed, Khaled Z.; Ibok, Effiong E.; Song, Miryeong; Yeap, Geoffrey; Xiang, Qi; Bang, David S.; Lin, Ming-Ren (1998). “Sub-100 nm nMOSFETs with direct tunneling thermal, nitrous and nitric oxides”. 56th Annual Device Research Conference Digest (Cat. No.98TH8373). pp. 10–11. doi:10.1109/DRC.1998.731099. ISBN 0-7803-4995-4. S2CID 1849364.

- Schwierz, Frank; Wong, Hei; Liou, Juin J. (2010). Nanometer CMOS. Pan Stanford Publishing. p. 17. ISBN 9789814241083. Archived from the original on 24 May 2020. Retrieved 11 October 2019.

- Wakabayashi, Hitoshi; Yamagami, Shigeharu; Ikezawa, Nobuyuki; Ogura, Atsushi; Narihiro, Mitsuru; Arai, K.; Ochiai, Y.; Takeuchi, K.; Yamamoto, T.; Mogami, T. (December 2003). Sub-10-nm planar-bulk-CMOS devices using lateral junction control. IEEE International Electron Devices Meeting 2003. pp. 20.7.1–20.7.3. doi:10.1109/IEDM.2003.1269446. ISBN 0-7803-7872-5. S2CID 2100267.

- “Still Room at the Bottom (nanometer transistor developed by Yang-kyu Choi from the Korea Advanced Institute of Science and Technology )”, Nanoparticle News, 1 April 2006, archived from the original on 6 November 2012

- Lee, Hyunjin; Choi, Yang-Kyu; Yu, Lee-Eun; Ryu, Seong-Wan; Han, Jin-Woo; Jeon, K.; Jang, D.Y.; Kim, Kuk-Hwan; Lee, Ju-Hyun; et al. (June 2006). “Sub-5nm All-Around Gate FinFET for Ultimate Scaling”. 2006 Symposium on VLSI Technology, 2006. Digest of Technical Papers. pp. 58–59. doi:10.1109/VLSIT.2006.1705215. hdl:10203/698. ISBN 978-1-4244-0005-8. S2CID 26482358.

- Patterson, Alan (12 December 2016), “TSMC Plans New Fab for 3nm”, EE Times, retrieved 22 July 2023

- Patterson, Alan (2 October 2017), “TSMC Aims to Build World’s First 3-nm Fab”, EE Times, retrieved 22 July 2023

- Zafar, Ramish (15 May 2019). “TSMC To Commence 2nm Research In Hsinchu, Taiwan Claims Report”. Wccftech.com. Archived from the original on 7 November 2020. Retrieved 6 December 2019.

“TSMC to start production on 5nm in second half of 2020, 3nm in 2022”. Techspot.com. 8 December 2019. Archived from the original on 19 December 2019. Retrieved 12 January 2020.