电子设计自动化(英语:Electronic design automation,缩写:EDA)是指利用计算机辅助设计(CAD)软件,来完成超大规模集成电路(VLSI)芯片的功能设计、综合、验证、物理设计(包括布局、布线、版图、设计规则检查等)等流程的设计方式。

EDA涵盖了电子设计、仿真、验证、制造全过程的所有技术,诸如:系统设计与仿真,电路设计与仿真,印制电路板(PCB)设计与校验,集成电路(IC)版图设计、验证和测试,数字逻辑电路设计,模拟电路设计,数模混合设计,嵌入式系统设计,软硬件协同设计,芯片上系统(SoC)设计,可编程逻辑器件(PLD)和可编程系统芯片(SOPC)设计,专用集成电路(ASIC)和专用标准产品(ASSP)设计技术等。高级硬件描述语言和IP芯核被广泛采用,使得电子设计方式以及电子系统的概念发生了根本性的改变。

IP是集成电路知识产权模块的简称,可以定义为“经过预先设计、预先验证,具有相对独立功能,可以重复使用在SoC和复杂ASIC中的电路模块”。按照其在设计流程中的位置,IP可分为三种:软核IP、固核IP和硬核IP。

软核IP是用可综合硬件描述语言描述的RTL级电路功能块,不涉及用与什么工艺相关的电路和电路元件实现这些描述。软核IP的设计周期短,设计投入少,由于不涉及物理实现,为后续设计留有很大的发挥空间;但同时也会有一定比例的后续工序无法适应软核IP设计,从而造成一定程度的软核IP修正,在性能上有较大的不可预知性。另外,软核IP在使用时需要冒相当大的知识产权保护风险。

硬核IP是经过布局、布线并针对某一特定工艺库优化过的网表或是物理级版图。硬核IP在功耗、尺寸等方面都做了充分的优化,有着很好的可预知性,但对工艺的依赖性使得其灵活性和可移植性都较差。 固核IP是已经基于一般工艺库进行了综合和布局的IP核,通常以网表的形式提交客户使用。因此其在结构、面积和性能的安排上都已进行了优化。固核IP是介于软核和硬核之间的一个折中方案。

现今数字电路非常模组化(参见集成电路设计、设计收敛、设计流程 (EDA)),产线最前端将设计流程标准化,把设计流程区分为许多“细胞”(cells),而暂不考虑技术,接着细胞则以特定的集成电路技术实现逻辑或其他电子功能。制造商通常会提供组件库(libraries of components),以及符合标准模拟工具的模拟模型给生产流程。模拟 EDA 工具较不模组化,因为它需要更多的功能,零件间需要更多的互动,而零件一般说较不理想。

在电子产业中,由于半导体产业的规模日益扩大,EDA 扮演越来越重要的角色。使用这项技术的厂商多是从事半导体器件制造的代工制造商,以及使用 EDA 模拟软件以评估生产情况的设计服务公司。EDA 工具也应用在现场可编程逻辑门阵列的程序设计上。

历史与发展

在电子设计自动化出现之前,设计人员必须手工完成集成电路的设计、布线等工作,这是因为当时所谓集成电路的复杂程度远不及现在。工业界开始使用几何学方法来制造用于电路光绘(photoplotter)的胶带。

到了1970年代中期,开发人员尝试将整个设计过程自动化,而不仅仅满足于自动完成掩膜草图。第一个电路布局、布线工具研发成功。设计自动化研讨会(Design Automation Conference)在这一时期被创立,旨在促进电子设计自动化的发展。

电子设计自动化发展的下一个重要阶段以卡弗尔·米德(Carver Mead)和琳·康维于1980年发表的论文《超大规模集成电路系统导论》(Introduction to VLSI Systems)为标志。这一篇具有重大意义的论文提出了通过编程语言来进行芯片设计的新思想。如果这一想法得到实现,芯片设计的复杂程度可以得到显著提升。这主要得益于用来进行集成电路逻辑仿真、功能验证的工具的性能得到相当的改善。随着计算机仿真技术的发展,设计项目可以在构建实际硬件电路之前进行仿真,芯片布局、布线对人工设计的要求降低,而且软件错误率不断降低。直至今日,尽管所用的语言和工具仍然不断在发展,但是通过编程语言来设计、验证电路预期行为,利用工具软件综合得到低抽象级(或称“后端”)物理设计的这种途径,仍然是数字集成电路设计的基础。

从1981年开始,电子设计自动化逐渐开始商业化。1984年的设计自动化会议(Design Automation Conference)上还举办了第一个以电子设计自动化为主题的销售展览。Gateway设计自动化在1986年推出了一种硬件描述语言Verilog,这种语言在现在是最流行的高级抽象设计语言。1987年,在美国国防部的资助下,另一种硬件描述语言VHDL被创造出来。现代的电子设计自动化设计工具可以识别、读取不同类型的硬件描述。[5]根据这些语言规范产生的各种仿真系统迅速被推出,使得设计人员可对设计的芯片进行直接仿真。后来,技术的发展更侧重于逻辑综合。

进入21世纪之后,一方面,三家大EDA公司(Synopsys、Cadence、Mentor)通过多次并购整合,完善设计全流程,奠定了三巨头竞争格局。另一方面,EDA公司开始深入制造领域,发展出了OPC等制造EDA的工具以及可制造性设计(DFM)工具。同时,晶圆厂成为了EDA的深度用户,不仅在制造方面需要使用EDA工具,在标准单元库、SRAM设计上都需要使用。此外,领先晶圆厂每两年开发一代工艺,其中EDA的整套设计流程需要在新工艺上验证。EDA也开始在早期工艺研发中介入,帮助解决更复杂的设计规则以及种种难题。晶圆厂提供的Signoff签核流程决定了设计公司设计出的芯片能否在晶圆制造厂顺利生产。而Signoff签核的主要工具就是EDA,可以说EDA是架起了设计与制造沟通的桥梁。同时,先进工艺不断迭代也驱动了EDA的创新。可见,此时此刻EDA在产业链已经有着举足轻重的作用。

目前的数字集成电路的设计都比较模块化(参见集成电路设计、设计收敛(Design closure)和设计流(Design flow (EDA)))。半导体器件制造工艺需要标准化的设计描述,高抽象级的描述将被编译为信息单元(cell)的形式。设计人员在进行逻辑设计时尚无需考虑信息单元的具体硬件工艺。利用特定的集成电路制造工艺来实现硬件电路,信息单元就会实施预定义的逻辑或其他电子功能。半导体硬件厂商大多会为它们制造的元件提供“元件库”,并提供相应的标准化仿真模型。相比数字的电子设计自动化工具,模拟系统的电子设计自动化工具大多并非模块化的,这是因为模拟电路的功能更加复杂,而且不同部分的相互影响较强,而且作用规律复杂,电子元件大多没有那么理想。Verilog AMS就是一种用于模拟电子设计的硬件描述语言。[7]此外,设计人员可以使用硬件验证语言来完成项目的验证工作目前最新的发展趋势是将集描述语言、验证语言集成为一体,典型的例子有SystemVerilog。

随着集成电路规模的扩大、半导体技术的发展,EDA的重要性急剧增加。这些工具的使用者包括半导体器件制造中心的硬件技术人员,他们的工作是操作半导体器件制造设备并管理整个工作车间。一些以设计为主要业务的公司,也会使用电子设计自动化软件来评估制造部门是否能够适应新的设计任务。电子设计自动化工具还被用来将设计的功能导入到类似现场可编程逻辑门阵列的半定制可程式逻辑装置,或者生产全定制的特殊应用积体电路。

现况

现今数位电路非常模组化(参见集成电路设计、设计收敛、设计流程 (EDA)),产线最前端将设计流程标准化,把设计流程区分为许多“细胞”(cells),而暂不考虑技术,接著细胞则以特定的集成电路技术实现逻辑或其他电子功能。制造商通常会提供组件库(libraries of components),以及符合标准模拟工具的模拟模型给生产流程。类比EDA工具较不模组化,因为它需要更多的功能,零件间需要更多的互动,而零件一般说较不理想。

在电子产业中,由于半导体产业的规模日益扩大,EDA扮演越来越重要的角色。使用这项技术的厂商多是从事半导体器件制造的代工制造商,以及使用EDA模拟软体以评估生产情况的设计服务公司。EDA工具也应用在现场可编程逻辑门阵列的程序设计上。

如今的集成电路,从系统架构开始,落实到功能的定义和实现,最终实现整个芯片的版图设计与验证,是一项复杂的系统工程,集成了人类智慧的最高成果。以华为2020年最新的7nm麒麟990芯片来说,其中集成了103亿颗晶体管,若没有EDA辅助,设计这样复杂的电路并保证良率是无法想象的。可见EDA这套工具,赋能了集成电路设计与制造的创新,当之无愧的站在了产业链的顶端。

未来发展趋势

目前,EDA在国际市场上已经发展成为了相对成熟的产业,而每年增长率只有10%左右。但有业内人士分析认为,这并不代表日后发展的机会在变小,在未来 EDA 的发展趋势可能有:

- AI赋能

- EDA上云

- 异构集成

另一方面,由于美国对华科技禁令的影响,中国将逐渐放弃自美国引进全套EDA服务,加上开发方向的转变,产业发展转而投向中国自研EDA的高成长市场,为了保住中国的利润,美国几大EDA公司甚至展开了竞争,为此大举投资中国EDA新势力并设立各自的合作据点。科技产业的变化,也带动起步中的中国EDA品牌的往新的大方向前进,并随著技术落实而逐渐获利后,EDA为美国垄断的格局将会出现变化。

重点软体分类

设计

- 高级综合(或行为综合、算法综合)——高级设计描述(例如在C/C++中)转换为RTL。

- 逻辑综合-将RTL设计描述(例如用Verilog或VHDL编写)转换为逻辑门的离散netlist。

- 原理图捕获-用于标准单元数字,模拟,rf类捕获CIS在Orcad由Cadence和ISIS在Proteus

- 布局——通常是由模式驱动的布局,比如在Orcad中的Cadence布局,在Proteus中的ARES布局

模拟

分析及验证

制造制备

芯片之母

EDA被誉为“芯片之母”,是电子设计的基石产业。拥有百亿美金的EDA市场构筑了整个电子产业的根基,可以说“谁掌握了EDA,谁就有了芯片领域的主导权。”

对于中国来说,EDA芯片设计软件的国产化对于芯片领域的突破意义与光刻机制造同等重要。

EDA 行业竞争格局

EDA 行业具有较高壁垒

EDA 行业具有较高壁垒。EDA 行业是典型的技术驱动行业,对研发投入、研发人 员、用户协同等都提出了较高要求,具有较高行业壁垒。

技术壁垒:EDA 是算法密集型的大型工业软件系统,需要强大的数学基础理 论支撑,且对算法的要求较高。此外,EDA 工具要尽可能准确的在软件中重 现和拟合现实中的物理和工艺问题,设计工具和制造工艺紧密结合的重要性 愈发突出。EDA 企业保持长久竞争力需要高强度、长周期的研发投入获得较 长时间的技术积累和专利积累,易形成较高的技术壁垒。

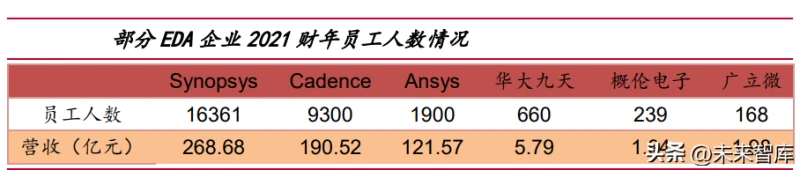

人才储备壁垒:EDA 开发过程需要计算机、数学、物理、电子电路、工艺等 多种学科和专业的高端人才,对综合技能要求很高,企业的人才储备决定其 是否能够在行业中持续发展。行业头部公司均拥有经验丰富、实力雄厚的研 发队伍,其知名度、成熟培训体系等也能够持续吸引人才加入,研发人员规 模领先,形成了人才壁垒。2021 财年末,海外 EDA 巨头 Synopsys、Cadence 员工人数分别为 16361、9300,是支撑其在全球 EDA 市场获得较高市占率的 重要因素之一。

用户协同壁垒:EDA 工具的技术开发和商业销售依托于制造、设计、EDA 行业 三方所形成的生态圈,需要产业链上下游的全力支持。国际 EDA 领域的领先 企业与全球领先的集成电路制造和设计企业具备长期合作基础,其 EDA 工具 工艺库信息完善,能够随先进工艺演进不断迭代,进一步巩固了竞争优势。 EDA 行业下游用户一旦确定了 EDA 供应商,短时间在内部更换 EDA 工具软件 的成本较大,因此集成电路制造与设计企业对合作 EDA 工具供应商粘性较强。

资金规模壁垒:为保持较高的行业竞争力,EDA 企业需要投入大量的研发支 出和并购支出,因此形成了较高的资金规模壁垒。海外 EDA 巨头 Synopsys、 Cadence 持续加大研发投入,近十年研发费用分别累计为 627.41 亿元、508.92 亿元,平均研发费用率分别为 34.56%、38.90%。

全球 EDA 行业高度集中

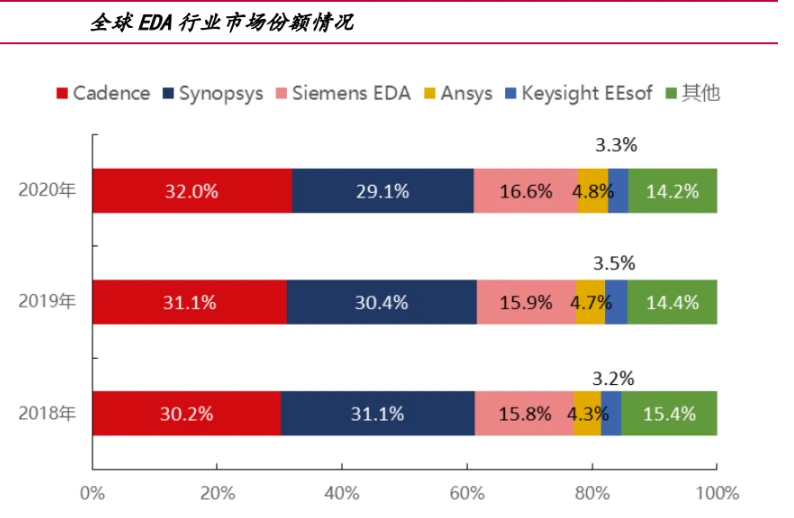

全球 EDA 行业高度集中,CR3 超过 77%。EDA 行业具有较高的技术、人才储备、 用户协同、资金规模等行业壁垒,经过 30 余年的行业整合发展,形成较高集中度的 行业竞争格局。新思科技(Synopsys)、铿腾电子(Cadence)、西门子 EDA(Siemens EDA)三家厂商是处于全球 EDA 行业第一梯队的巨头公司,具备对于半定制、全定制 IC 设计全流程的覆盖能力,能够为客户提供整套的 IC 设计工具,已建立起相当完善 的行业生态圈,形成了较高的行业壁垒和用户粘性,占据了全球主要的 EDA 市场。根 据赛迪顾问统计,2020 年新思科技(Synopsys)、铿腾电子(Cadence)、西门子 EDA (Siemens EDA)在全球 EDA 市场占有率分别为 29.1%、32.0%、16.6%,合计超过 77%。

ANSYS、是德科技也占据了较为突出的市场份额,CR5 约 85%。除新思科技、铿 腾电子、西门子EDA 三家国际 EDA 巨头外,ANSYS和是德科技(Keysight Technologies) 为代表的国际领先 EDA 公司,凭借其在细分领域取得的技术领先优势,在特定的设计 环节或特定领域形成了其垄断地位,已成功抢占了较为突出的市场份额。根据赛迪顾 问统计,2020 年 ANSYS、是德科技全球 EDA 市场市占率分别为 4.8%、3.3%,前五大 EDA 公司累计占有了超 85%的全球 EDA 市场份额。

除全球前五大 EDA 公司外,仍有相当数量的 EDA 公司。虽然全球 EDA 巨头具有 较高的竞争优势,但由于 EDA 工具的复杂性,不同厂商之间仍然各具差异化优势。一 些成长中的企业通过专注与快速迭代在细分市场实现局部竞争优势,主要采取了两种策略:一是优先突破关键环节核心工具,典型公司国际上还有 PDF Solutions 等, 国内有概伦电子、广立微等;二是优先突破部分设计应用全流程解决方案,典型公司 国际上有 SILVACO、Jedat Inc.等,国内有华大九天等。根据赛迪顾问统计,除全球 前五大 EDA 公司外,2020 年其他 EDA 公司共占有 14.2%的市场份额。

国内 EDA 市场也主要由三大巨头占据。1994 年“巴统”禁令取消,海外 EDA 三 巨头大举进入中国市场,以技术成熟、价格便宜、免费赠送、多方合作等策略,快速 获取市场份额,国产 EDA 发展受挫。2008 年后国家出台相关政策,国产 EDA 迎来发 展机遇,但受制于海外 EDA 龙头的深厚技术、经验积累,国内 EDA 市场仍主要由三大 巨头占据。根据赛迪智库统计,2020 年国际三大 EDA 巨头新思科技、铿腾电子和西门 子 EDA 在国内市场占据明显的头部优势,合计占领约 80%的市场份额;国产 EDA 厂商 华大九天市占率约 6%,处于国内市场第四位。

美国断供EDA软件,对中国芯片发展有什么影响?

EDA是芯片IC设计中不可或缺的重要部分,是一种广泛使用的技术的高级形式,属于芯片制造的上游产业,涵盖集成电路设计、布线、验证和仿真等所有流程。EDA被行业内称为“芯片之母”。目前,全球的EDA软件主要由Cadence、Synopsys、Mentor(被西门子收购)等三家美国企业垄断。称霸EDA市场的美国三巨头,牢牢占据了全球超过70%的市场份额,能够提供完整的EDA工具,覆盖集成电路设计与制造全流程或大部分流程。

当下,国内大多数芯片设计公司仍在采用进口的EDA工业软件来设计芯片,这也就导致了国内芯片设计领域难以实现真正意义上的国产化。一旦美国断供EDA软件,短时间内肯定会严重影响国内芯片企业的设计能力。

GAAFET晶体管技术是相对于FinFET晶体管更先进的技术,FinFET技术最多能做到3nm,而GAAFET可以实现2nm。氧化镓(Ga2O3)、金刚石则是被普遍关注的第四代半导体材料。

这四项技术是 42 个参与国在2021年12月会议上达成共识控制的项目之一。美国的出口管制涵盖了比国际协议更广泛的技术,包括用于生产半导体的额外设备、软件和技术。

美国商务部表示,此举涵盖的“新兴和基础技术”包括氧化镓和金刚石,因为“使用这些材料的设备显着增加了军事潜力”。